# **USER MANUAL**

# PMAC2

Programmable Multi-Axis Control

3Ax-602413-xUxx

January 28, 2003

# **Contents**

| Chapter<br>Number | Chapter/Paragraph Title         | Page<br>Numbe |

|-------------------|---------------------------------|---------------|

| Contents          |                                 | i             |

| Figures x         |                                 |               |

| _                 |                                 |               |

| Tables xi         |                                 |               |

|                   |                                 |               |

|                   |                                 |               |

|                   |                                 |               |

|                   |                                 |               |

|                   |                                 |               |

|                   | Introduction                    | 1-1           |

|                   |                                 |               |

| ī                 | PMAC Overview                   | 1.1           |

| 1                 | Flexibility                     |               |

|                   | Configuration For a Task        |               |

|                   | PMAC2 Is a Computer             |               |

| Ŋ                 | Manual Layout                   |               |

| 1                 | Conventions Used in This Manual |               |

|                   | Organization                    |               |

| 9                 | Safety Summary                  |               |

|                   | Keep Away From Live Circuits    |               |

|                   | Live Circuit Contact Procedures |               |

|                   | Electrostatic Sensitive Devices |               |

|                   | Magnetic Media                  |               |

| I                 | Related Technical Documentation |               |

|                   | Technical Support               |               |

|                   | By Telephone                    |               |

|                   | By FAX and E-Mail               | 1-6           |

|                   | Bulletin Board Service (BBS)    | 1-7           |

| PMAC2 Parameter Setup                                                                                                                                                                                                                                                                          | Hardware Setup                                    | 2-1 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----|

| Parameters to Set Up Per-Channel Hardware Signals 2-3 Parameters to Set Up Motor Operation 2-5 Activating the Motor 2-5 Does PMAC Commutate the Motor? 2-5 Command Output Address 2-6 Position-Loop Feedback Address 2-6 Velocity-Loop Feedback Address 2-6 Flag Address 2-7 Power-Up Mode 2-7 | PMAC2 Parameter Setup                             | 2-2 |

| Parameters to Set Up Motor Operation 2-5 Activating the Motor 2-5 Does PMAC Commutate the Motor? 2-5 Command Output Address 2-6 Position-Loop Feedback Address 2-6 Velocity-Loop Feedback Address 2-6 Flag Address 2-7 Power-Up Mode 2-7                                                       | Parameters to Set Up Global Hardware Signals      | 2-2 |

| Activating the Motor                                                                                                                                                                                                                                                                           | Parameters to Set Up Per-Channel Hardware Signals | 2-3 |

| Does PMAC Commutate the Motor?2-5Command Output Address2-6Position-Loop Feedback Address2-6Velocity-Loop Feedback Address2-6Flag Address2-7Power-Up Mode2-7                                                                                                                                    | Parameters to Set Up Motor Operation              | 2-5 |

| Command Output Address2-6Position-Loop Feedback Address2-6Velocity-Loop Feedback Address2-6Flag Address2-7Power-Up Mode2-7                                                                                                                                                                     | Activating the Motor                              | 2-5 |

| Position-Loop Feedback Address 2-6 Velocity-Loop Feedback Address 2-6 Flag Address 2-7 Power-Up Mode 2-7                                                                                                                                                                                       | Does PMAC Commutate the Motor?                    | 2-5 |

| Velocity-Loop Feedback Address2-6Flag Address2-7Power-Up Mode2-7                                                                                                                                                                                                                               | Command Output Address                            | 2-6 |

| Flag Address 2-7 Power-Up Mode 2-7                                                                                                                                                                                                                                                             | Position-Loop Feedback Address                    | 2-6 |

| Power-Up Mode                                                                                                                                                                                                                                                                                  | Velocity-Loop Feedback Address                    | 2-6 |

| 2 ( P 11040                                                                                                                                                                                                                                                                                    | Flag Address                                      | 2-7 |

| Commutation Parameters 2-7                                                                                                                                                                                                                                                                     | Power-Up Mode                                     | 2-7 |

|                                                                                                                                                                                                                                                                                                | Commutation Parameters                            | 2-7 |

| Setting Up PMAC2 for Direct PWM Control           | 3-1  |

|---------------------------------------------------|------|

| Introduction                                      | 3-1  |

| Direct PWM Control Of Amplifiers                  | 3-1  |

| Digital Current Loop Principle of Operation       | 3-2  |

| Frames of Reference                               | 3-2  |

| Working in the Field Frame                        | 3-2  |

| Analog Loops in the Stator Frame                  | 3-3  |

| Digital Loops in the Field Frame                  | 3-3  |

| Hardware Setup                                    | 3-4  |

| PWM Signal Outputs                                | 3-6  |

| ADC Interface Signals                             | 3-6  |

| PWM/ADC Phase Matching                            | 3-6  |

| Amplifier Enable and Fault Interface              | 3-7  |

| Supplemental Flags                                | 3-7  |

| Other Signals                                     | 3-7  |

| PMAC2 Parameter Setup                             | 3-8  |

| Parameters to Set up Global Hardware Signals      | 3-8  |

| PWM Frequency Control: I900, I906                 | 3-8  |

| Phase Clock Frequency Control: I901               | 3-8  |

| Servo Clock Frequency Control: I902               | 3-9  |

| Hardware Clock Frequency Control: 1903, 1908      | 3-9  |

| PWM Deadtime Control: I904, I908                  | 3-10 |

| Parameters to Set Up Per-Channel Hardware Signals | 3-10 |

| Parameters to Set Up Motor Operation              | 3-10 |

|                                                   |      |

| Commutation Enable: Ix01                   | 3-10 |

|--------------------------------------------|------|

| Command Output Address: Ix02               | 3-11 |

| Current Feedback Address: Ix82             | 3-11 |

| Current Feedback Mask Word: Ix84           | 3-12 |

| PWM Scale Factor: Ix66                     | 3-12 |

| Servo Loop Output Limit: Ix69              | 3-12 |

| Continuous Current Limit: Ix57             | 3-14 |

| Integrated Current Limit: Ix58             | 3-14 |

| Commutation Cycle Size: Ix70, Ix71         | 3-14 |

| Commutation Phase Angle: Ix72              | 3-14 |

| Commutation Feedback Address: Ix83         | 3-15 |

| Using Direct PWM for Brush Motor Control   | 3-15 |

| Hardware Connection                        | 3-16 |

| I-Variable Setup                           | 3-16 |

| Testing PWM and Current Feedback Operation | 3-17 |

| Introduction                               | 3-17 |

| Purpose                                    | 3-18 |

| Preparation                                | 3-18 |

| Position Feedback and Polarity Test.       | 3-19 |

| PWM Output & ADC Input Connection.         | 3-20 |

| PWM/ADC Phase Match                        | 3-20 |

| Synchronous Motor Stepper Action           | 3-21 |

| Current Loop Polarity Check                | 3-21 |

| Troubleshooting                            | 3-21 |

| Voltage Six-Step Test                      | 3-22 |

| What To Look For                           | 3-22 |

| Executing the Test                         | 3-22 |

| Action To Take                             | 3-23 |

| Example                                    | 3-23 |

| Cleaning Up                                | 3-24 |

| Debugging                                  | 3-24 |

| Establishing Basic Current Loop Operation  | 3-25 |

| Purpose                                    | 3-25 |

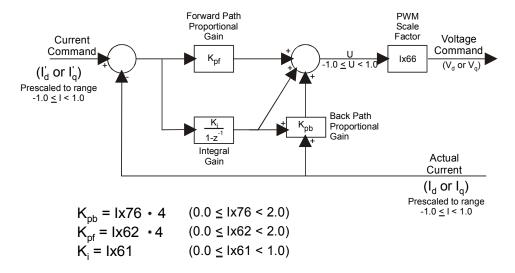

| Digital Current Loop Gains                 | 3-25 |

| Preparation                                | 3-26 |

| Executing the Current-Loop Test            | 3-27 |

| Clean-Up                                   | 3-27 |

| Setting Up PMAC2 for Sine-Wave Output Control          | 4-1 |

|--------------------------------------------------------|-----|

| How to Set Up the Commutation Scheme                   | 4-1 |

| Hardware Setup                                         |     |

| DAC Output Signals                                     | 4-1 |

| Amplifier Enable and Fault Interface                   | 4-2 |

| Encoder Feedback                                       | 4-2 |

| Supplemental Flags                                     | 4-2 |

| Other Signals                                          | 4-2 |

| PMAC2 Parameter Setup                                  | 4-3 |

| Parameters to Set Up Global Hardware Signals           | 4-3 |

| Phase Clock Frequency Control: I900, I901              | 4-3 |

| Servo Clock Frequency Control: I902                    | 4-4 |

| Hardware Clock Frequency Control: I903, I907           | 4-4 |

| DAC Strobe Control: I905, I909                         | 4-4 |

| Parameters to Set Up Per-Channel Hardware Signals      | 4-5 |

| Encoder Decode Control: I9n0                           | 4-5 |

| Output Mode Control: I9n6                              | 4-5 |

| Output Inversion Control: I9n7                         | 4-5 |

| Parameters to Set Up Motor Operation.                  |     |

| Commutation Enable: Ix01                               | 4-5 |

| Command Output Address: Ix02                           | 4-6 |

| Commutation Cycle Size: Ix70, Ix71                     | 4-6 |

| Commutation Phase Angle: Ix72                          |     |

| Commutation Feedback Address: Ix83                     | 4-7 |

| Establishing Basic Output Operation                    |     |

| Executing the Test                                     | 4-8 |

| Verifying Basic Operation                              | 4-8 |

| Evaluating the Polarity Match                          | 4-8 |

|                                                        |     |

| Setting Up PMAC2 Commutation (Direct PWM or Sine Wave) | 5-1 |

| Operation of the Digital Current Loops                 | 5-1 |

| Confirming Commutation Polarity Match                             | 5-1  |

|-------------------------------------------------------------------|------|

| Synchronous Motor Test                                            | 5-1  |

| Asynchronous Motor Test                                           | 5-2  |

| Correcting Polarity Mismatch, Synchronous and Asynchronous Motors | 5-2  |

| Establishing A Phase Reference (Synchronous Motors Only)          | 5-3  |

| Purpose                                                           | 5-3  |

| Preparation                                                       | 5-3  |

| Current Command Six-Step Test                                     | 5-5  |

| Direction Balance Fine Phasing Test                               | 5-6  |

| Preparation                                                       | 5-6  |

| Executing the Test                                                | 5-7  |

| Using the Test Results for Absolute Sensor                        | 5-7  |

| Using the Test Results for Incremental Index Pulse                | 5-8  |

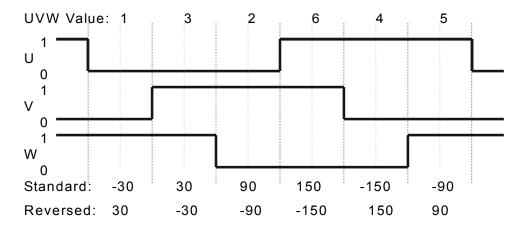

| Using Hall-Effect Sensors for Phase Reference                     | 5-8  |

| Preparation                                                       | 5-9  |

| Executing the Test                                                | 5-9  |

| Using the Test Results                                            | 5-10 |

| Overall Procedure Summary                                         | 5-12 |

| PLC-Based Hall-Effect Reference                                   |      |

| Power-On Phasing Search                                           | 5-13 |

| Two-Guess Phasing Search                                          | 5-13 |

| Stepper-Motor Phasing Search                                      | 5-14 |

| Custom Phasing Search Methods                                     | 5-15 |

| Final Phase Correction with Index Pulse                           | 5-17 |

| What To Do Next                                                   | 5-17 |

|                                                                   |      |

| Setting Up PMAC2 For Velocity or Torque Control  | 6-1 |

|--------------------------------------------------|-----|

| Single Output Command                            | 6-1 |

| Hardware Setup                                   | 6-1 |

| DAC Output Signals                               | 6-1 |

| Amplifier Enable and Fault Interface             | 6-2 |

| Encoder Feedback                                 | 6-2 |

| Supplemental Flags                               | 6-2 |

| Other Signals                                    | 6-2 |

| PMAC2 Parameter Setup                            | 6-2 |

| Parameters to Set Up Global Hardware Signals     | 6-2 |

| Servo Clock Frequency Control: I900, I901, I902. | 6-2 |

| Hardware Clock Frequency Control: I903, I907     | 6-3 |

| DAC Strobe Control: I905, I909                    | 6-4 |

|---------------------------------------------------|-----|

| Parameters to Set Up Per-Channel Hardware Signals | 6-4 |

| Encoder Decode Control: I9n0                      | 6-4 |

| Output Mode Control: 19n6                         | 6-4 |

| Output Inversion Control: I9n7                    | 6-4 |

| Parameters to Set Up Motor Operation              | 6-5 |

| Commutation Enable: Ix01                          | 6-5 |

| Command Output Address: Ix02                      | 6-5 |

### Setting Up PMAC2 For Pulse-and-Direction Control.......7-1 PFM Clock Frequency Control: 1903, 1907, 1993.

| Executing the Open-Loop Test                                                                                                                                                                                                                |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Troubleshooting the Open-Loop Test                                                                                                                                                                                                          |  |

| Executing the Closed-Loop Test                                                                                                                                                                                                              |  |

| Troubleshooting the Closed Boop Test                                                                                                                                                                                                        |  |

| Using PMAC2 with MACRO Interface                                                                                                                                                                                                            |  |

| Introduction                                                                                                                                                                                                                                |  |

| Hardware Setup                                                                                                                                                                                                                              |  |

| Parameter Setup                                                                                                                                                                                                                             |  |

| Ring Configuration                                                                                                                                                                                                                          |  |

| I995: MACRO Role/Status                                                                                                                                                                                                                     |  |

| I996: MACRO Node Activation                                                                                                                                                                                                                 |  |

| I1000: MACRO Node Auxiliary Function Enable                                                                                                                                                                                                 |  |

| I1001: MACRO Ring Check Control                                                                                                                                                                                                             |  |

| I1002: MACRO Node Protocol Type Control                                                                                                                                                                                                     |  |

| I1003: MACRO Auxiliary Timeout Control                                                                                                                                                                                                      |  |

| Ring Cycle Frequency Control                                                                                                                                                                                                                |  |

| Feedback Processing in Encoder Conversion Table                                                                                                                                                                                             |  |

| Type 0 Nodes                                                                                                                                                                                                                                |  |

| Type 1 Nodes                                                                                                                                                                                                                                |  |

| Both Protocol Types                                                                                                                                                                                                                         |  |

|                                                                                                                                                                                                                                             |  |

|                                                                                                                                                                                                                                             |  |

| _                                                                                                                                                                                                                                           |  |

|                                                                                                                                                                                                                                             |  |

| •                                                                                                                                                                                                                                           |  |

| Feedback Address I-variables: Ix03, Ix04  E. Command Output Address I-variables: Ix02  Flag Address I-variables: Ix25  Commutation Position Feedback Address: Ix83  Commutation Cycle Size: Ix70, Ix71  Current Loop Feedback Address: Ix82 |  |

|                                                                                                                                                                                                                                             |  |

| Setting Up PMAC2 for MLDT Feedback                                                                                                                                                                                                          |  |

| Introduction                                                                                                                                                                                                                                |  |

| Interface Type                                                                                                                                                                                                                              |  |

| Signal Formats                           | 9-1  |

|------------------------------------------|------|

| Hardware Setup                           | 9-2  |

| PMAC2 Hardware-Control Parameter Setup   | 9-3  |

| PFMCLK Frequency: I903 & I907            | 9-3  |

| PFM Output Frequency: Mn07               | 9-3  |

| PFM Pulse Width: I904 & I908             | 9-4  |

| FM Format Select: I9n6                   | 9-4  |

| MLDT Feedback Select: I9n0               | 9-5  |

| PMAC2 Conversion Table Processing Setup  | 9-5  |

| Method and Address: Entry First Line     | 9-5  |

| Bits Enabled: Entry Second Line          | 9-5  |

| Maximum Change: Entry Third Line         | 9-5  |

| Table Result Register                    | 9-6  |

| Example                                  |      |

| PMAC2 Servo Loop I-Variable Setup        | 9-6  |

| Position Loop Feedback Address: Ix03     | 9-6  |

| Velocity Loop Feedback Address: Ix04     |      |

| Master Position Address: Ix05            |      |

| Absolute Power-Up Position Address: Ix10 |      |

| Example                                  |      |

| Scaling the Feedback Units               |      |

| Motor Units                              |      |

| Axis User Units                          |      |

| PMAC2 General Purpose I/O Use            | 10-1 |

| JIO Port                                 | 10-1 |

| Hardware Characteristics                 |      |

| Suggested M-Variables                    | 10-1 |

| Direction Control                        |      |

| Inversion Control                        |      |

| Alternate Uses                           |      |

| Multiplexer Port (JTHW)                  |      |

| Hardware Characteristics                 |      |

| Suggested M-Variables                    |      |

| Direction Control                        |      |

| Inversion Control                        |      |

| Alternate Uses                           |      |

| JANA Port                                |      |

|                                          |      |

| Hardware Characteristics                         | 10-6  |

|--------------------------------------------------|-------|

| Multiplexing Principle                           |       |

| Analog Data Table                                |       |

| Servo Feedback Use                               |       |

| Absolute Power-On Position                       | 10-11 |

|                                                  |       |

|                                                  |       |

|                                                  |       |

|                                                  |       |

|                                                  |       |

| H. A. B. W. C. F. A. BMACO                       | 11.1  |

| Using the Position Compare Feature on PMAC2      | 11-1  |

|                                                  |       |

| Software-Configurable Hardware Registers         | 11-1  |

| Principle of Operation                           | 11-2  |

| Scaling and Offset of Position Compare Registers | 11-3  |

| Initial Setup                                    | 11-3  |

| Setting Up for a Single Pulse Output             | 11-3  |

| Setting Up for Multiple Pulse Outputs            | 11-4  |

| Example                                          | 11-5  |

| Converting from Motor and Axis Coordinates       | 11-5  |

|                                                  |       |

|                                                  |       |

|                                                  |       |

|                                                  |       |

| Z                                                |       |

|                                                  |       |

| Using the PMAC2 to Interrupt the Host Computer   | 12-1  |

|                                                  |       |

| Programmable interrupt Controller (PIC) | 12-1 |

|-----------------------------------------|------|

| Interrupt Controller Structure          | 12-1 |

| PIC Registers                           | 12-2 |

| Interrupt Source Signals                |      |

# **Figures**

| Figure<br>Number | Figure Title                                    | Page<br>Number |

|------------------|-------------------------------------------------|----------------|

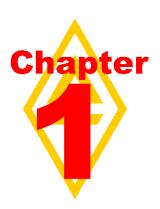

| Figure 1-1.      | PMAC2 Block Diagram                             | 1-1            |

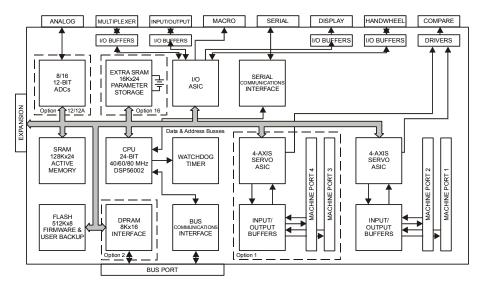

| Figure 1-2.      | PMAC2 Gate Array IC                             | 1-2            |

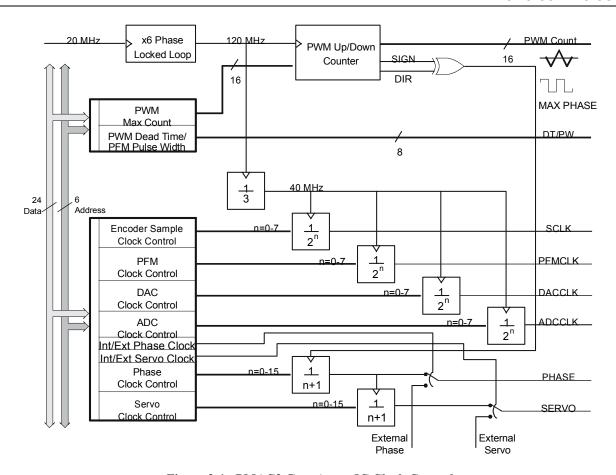

| Figure 2-1.      | PMAC2 Gate Array IC Clock Control               | 2-3            |

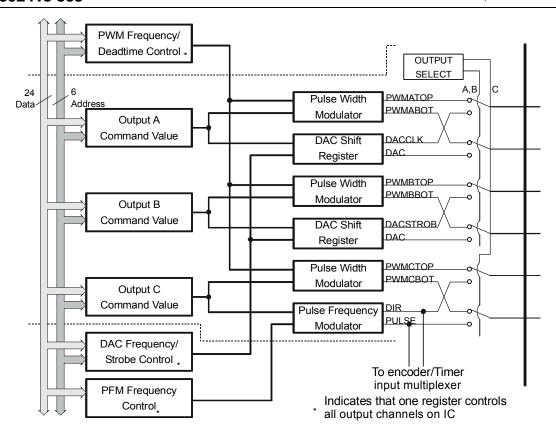

| Figure 2-2.      | PMAC2 Gate Array IC Output Channel              | 2-4            |

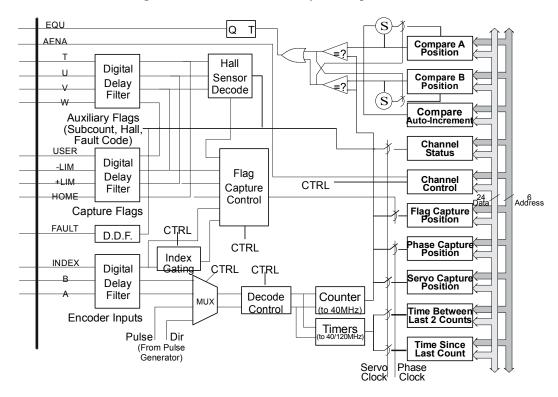

| Figure 2-3.      | PMAC2 Gate Array IC Encoder/Flag Channel        | 2-4            |

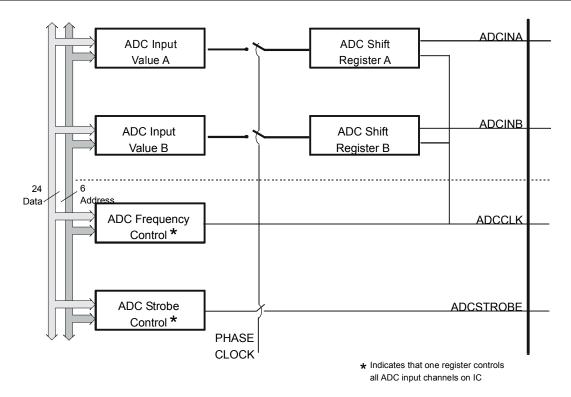

| Figure 2-4.      | PMAC2 Gate Array IC Input Channel               | 2-5            |

| Figure 2-5.      | DSP Gate Command Output Registers               | 2-6            |

| Figure 3-1.      | PMAC/PMAC2 Commutation with Analog Current Loop | 3-3            |

| Figure 3-2.      | PMAC2 Commutation with Digital Current Loop     | 3-4            |

| Figure 3-3.      | Digital PWM Generation (Per Phase)              | 3-13           |

| Figure 3-4.      | PMAC2 Digital Current Loop                      | 3-26           |

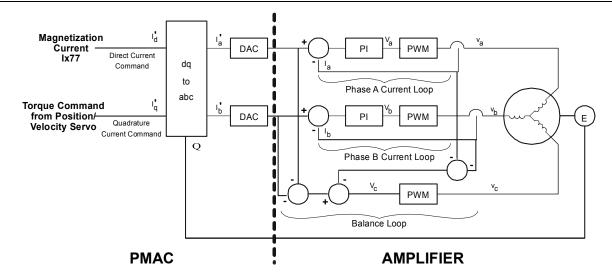

| Figure 4-1.      | PMAC/PMAC2 Commutation with Analog Loop         | 4-2            |

| Figure 4-2.      | Hall-Effect Waveforms With Zero Offset          | 5-11           |

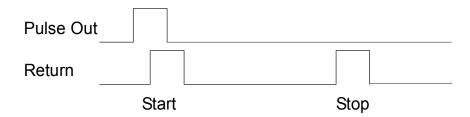

| Figure 9-1.      | RPM Signal Format                               | 9-2            |

| Figure 9-2.      | DPM Signal Format                               | 9-2            |

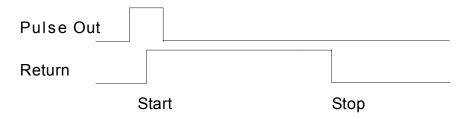

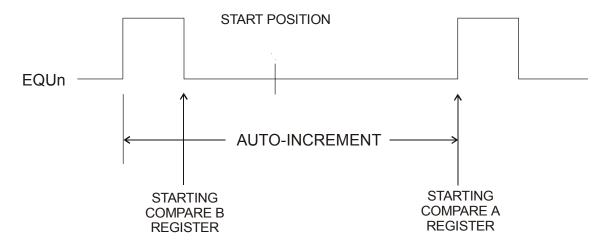

| Figure 11-1      | . Compare Function                              | 11-3           |

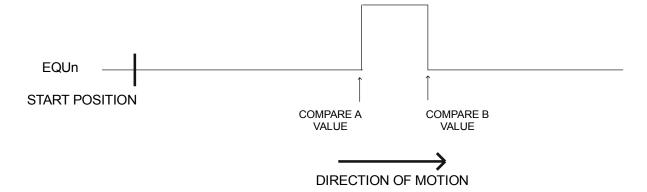

| Figure 11-2      | . Setup For Multiple Pulses                     | 11-4           |

# **Tables**

| Table<br>Number                                    | Table Title        | Page<br>Number |

|----------------------------------------------------|--------------------|----------------|

| Table 3-1. PWM Command Output Addresses (Y-re      | egisters)          | 3-11           |

| Table 3-2. MACRO Ix02 Values                       |                    | 3-11           |

| Table 3-3. ADC Current Feedback Addresses (Y-reg   | gisters)           | 3-11           |

| Table 3-4. MACRO Ix82 Values                       |                    | 3-12           |

| Table 3-5. Commutation Position Feedback Address   | sses (X-registers) | 3-15           |

| Table 3-6. MACRO Type 0 Or Type 1 Protocol Ix83    | 33 Values          | 3-15           |

| Table 3-7. Mapping The Image Registers             |                    | 3-18           |

| Table 3-8. Commutation Polarity Match Sample Tes   | st                 | 3-23           |

| Table 3-9. Commanded direct current registers      |                    | 3-27           |

| Table 3-10. Actual direct current registers        |                    | 3-27           |

| Table 4-1. DAC An Command Output Addresses (Y      | 7-registers)       | 4-6            |

| Table 4-2. MACRO Command Output Registers          |                    | 4-6            |

| Table 4-3. Commutation Position Feedback Address   | ses (X-registers)  | 4-7            |

| Table 4-4. MACRO Commutation Feedback Register     | ters               | 4-7            |

| Table 5-1. Phase Position Angle Registers          |                    | 5-4            |

| Table 5-2. Direct Integrator Output Registers      |                    | 5-6            |

| Table 5-3. Quadrature Integrator Output Registers  |                    | 5-6            |

| Table 5-4. The Values Of M124 Through M128 For     | r Each Position    | 5-10           |

| Table 6-1. DACnA Command Output Addresses (Y-      | -registers)        | 6-5            |

| Table 6-2. Type 0 MACRO Ix02 values                |                    | 6-5            |

| Table 6-3. Type 1 MACRO Ix02 values                |                    | 6-5            |

| Table 7-1. C Command Register Addresses            |                    | 7-6            |

| Table 7-2. Ix02 Required Values                    |                    | 7-6            |

| Table 7-3. Counters and Timer Sets Addresses       |                    | 7-7            |

| Table 7-4. Configuration Of The Encoder Conversio  |                    |                |

| Table 8-1. Setup Words For Each Node               |                    | 8-5            |

| Table 8-2. Command Outputs To MACRO Registers      | <sup>7</sup> S     | 8-8            |

| Table 8-3. Commutation Position Feedback Address   | s                  | 8-9            |

| Table 10-1. The A/D Converter Data Table           |                    | 10-6           |

| Table 10-2. Cycling Through All 8 Pairs Of ADCs In | In Unsigned Mode   | 10-7           |

| Table 10-3. Values Of Ix10 To Be Used For Each In  | nput               | 10-11          |

# Introduction

### **PMAC Overview**

The Delta Tau Data Systems, Inc. Programmable Multi-Axis Controller2 (PMAC2) is a family of high-performance servo motion controllers capable of commanding up to eight axes of motion simultaneously with a high level of sophistication. Through the power of a Digital Signal Processor (DSP), PMAC2 offers a price/performance ratio for multi-axis control that was not previously available. Motorola's DSP56002 is the CPU for PMAC2, and it handles all the calculations for all eight axes.

There are six hardware versions of PMAC2: the PMAC2-PC, the PMAC2-PC Ultralite, the PMAC2-Lite, the PMAC2-VME, the PMAC2-VME Ultralite, and the MiniPMAC2. These cards differ from each other in their form factor, the nature of the bus interface, and in the availability of certain I/O ports. All versions of the card have virtually identical on-board firmware, so PMAC2 programs written for one version will run on any other version.

Any version of PMAC2 may run as a standalone controller, or it may be commanded by a host computer, either over a serial port or over a bus port.

Figure 1-1. PMAC2 Block Diagram

### **Flexibility**

As a general purpose controller, PMAC2 can serve in a wide variety of applications, from those requiring sub-microinch precision to those needing hundreds of kilowatts or horsepower. Its diverse uses include robotics, machine tools, paper and lumber processing, assembly lines, food processing, printing, packaging, material handling, camera control, automatic welding, silicon wafer processing, laser cutting, and many others.

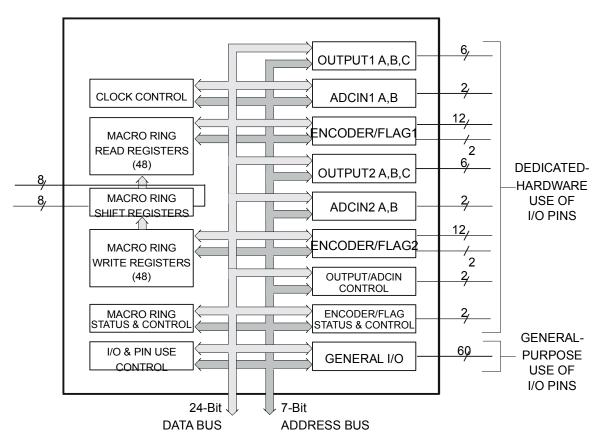

Figure 1-2. PMAC2 Gate Array IC

### **Configuration For a Task**

PMAC2 is configured for a particular application by choice of the hardware set (through options and accessories), configuration of parameters, and the writing of motion and PLC programs. Each PMAC2 possesses firmware capable of controlling eight axes. The eight axes can be all associated together for completely coordinated motion; each axis can be put in its own coordinate system for eight completely independent operations; any intermediate arrangement of axes into coordinate systems is also possible.

The PMAC2 CPU communicates with the axes through specially designed custom gate array ICs, referred to as DSPGATES. Each of these ICs can handle four analog output channels, four encoders as input, and four analog-derived inputs from accessory boards. One PMAC2 can utilize from one to four of these gate array ICs, so specifying the hardware configuration amounts to counting the numbers and types of inputs and outputs. Up to 16 PMAC2 may be ganged together with complete synchronization, for a total of 128 axes.

### PMAC2 Is a Computer

It is important to realize that PMAC2 is a full computer in its own right, capable of standalone operation with its own stored programs. Furthermore, it is a real-time, multitasking computer that can prioritize tasks and have the higher priority tasks pre-empt those of lower priority (most personal computers are not capable of this). Even when used with a host computer, the communications should be thought of as those from one computer to another, not as computer to peripheral. In these applications, the ability to run multiple tasks simultaneously, properly prioritized, can take a tremendous burden off the host computer (and its programmer!), both in terms of processor time, and of task-switching complexity.

# **Manual Layout**

This manual provides a quick step-by-step guide for the beginner setting up a typical system, as well as explaining how to use the various features available on PMAC2. It is organized by subject (safety, I/O, servos, trajectories, etc.) to allow quick access by the area of concern. The subjects are ordered by the typical sequence of events a user will go through to set up a system.

The manual organizes the commands in alphabetical order, and the variables, registers, jumpers and connectors in numerical order. There is extensive cross-referencing between the chapters. Any variable, command, register, jumper, or connector mentioned in chapter 2 is covered in more detail in the appropriate reference chapters.

As you read through the chapters, you may well find topics or depth of coverage that you do not need at the time. Simply skip these chapters and proceed to a chapter that is of more immediate use to you.

This manual assumes the system integrator who is responsible for this installation knows the basics of working in a Microsoft® Windows environment and has more than a basic understanding of electronics, machine tool technology, and the PMAC2 motion control board. If any questions about a particular aspect of the installation arise, do not attempt the task until a thorough understanding is gained. Feel free to contact Delta Tau Data Systems, Inc. technical support at any time during installation. Refer to the Technical Support section below for information on contacting our technical support department.

### **Conventions Used in This Manual**

The following conventions are used throughout the manual:

<ENTER>

<CTRL+F4>

OPEN PROGRAM

Italic text inside arrows is used to represent keyboard keys or key combinations.

Mono-spaced is used for code listings.

Information which, if not observed, may cause serious injury or death.

Information which, if not observed, may cause damage to equipment or software.

A note concerning special functions or information of special interest.

Electrostatic Sensitive Device. Use ESD control measures when handling, packing, and shipping (reference Appendix A).

### **Organization**

**Chapter 1 - Introduction:** This section gives a brief explanation of what PMAC2 does, the layout of the manual, general safety recommendations, related technical documentation, and product support information

**Chapter 2 - Basic Motor Setup on PMAC2:** This chapter provides hardware and software configuration to specify a specific mode of operation

**Chapter 3 - Setting Up PMAC2 for Direct PWM Control:** This chapter details how to perform digital current loop closure to manually set up hardware and software features properly.

**Chapter 4 - Setting Up PMAC2 for Sine-Wave Output Control:** This chapter provides information on how to set up the commutation scheme if PMAC2 is performing the commutation for a motor, but not the digital current loop.

Chapter 5 – Setting Up PMAC2 Commutation (Direct PWM or Sine Wave): This chapter details how to confirm the results of the synchronous motor polarity match tested in previous sections, as well as how to test the polarity for asynchronous induction motors.

**Chapter 6 - Setting Up PMAC2 For Velocity or Torque Control:** This chapter explains velocity or torque commands, typically encoded as an analog signal voltage level, required when PMAC2 is not performing the commutation for a motor.

Chapter 7 – Setting Up PMAC2 For Pulse-and-Direction Control: This chapter details the procedures for commanding stepper-motor drives that require pulse-and-direction format input, or stepper-replacement servo drives either in open-loop or in closed-loop fashion.

**Chapter 8 - Using PMAC2 with MACRO Interface:** This chapter describes the MACRO (Motion and Control Ring Optical) ring interface between PMAC2 and drives and I/O modules, and how it can greatly simplify the wiring of a motion control or I/O system.

Chapter 9 - Setting Up PMAC2 for MLDT Feedback: This chapter details providing direct interface to magnetostrictive linear displacement transducers (MLDTs), to provide absolute position information in rugged environments.

**Chapter 10 – PMAC2 General Purpose I/O Use:** This chapter describes the JIO port's 32 discrete digital I/O lines and provides information for configuring them individually for input or output using an inverting or non-inverting format.

Chapter 11 – Using the Position Compare Feature on PMAC2: This chapter explains the position compare feature on PMAC2 and describes how it provides a very fast and very accurate compare output function based on the actual position counter.

Chapter 12 - Using the PMAC2 to Interrupt the Host Computer: This chapter describes the procedures that allow PMAC2 to interrupt the host computer over the PC bus using any of eight built-in programmable interrupt controller (PIC) signals.

# **Safety Summary**

The following are general safety precautions not related to any specific procedures and therefore may not appear elsewhere in this publication. These are recommended precautions that personnel must understand and apply during many phases of operation and maintenance.

### **Keep Away From Live Circuits**

Do not replace components or make adjustments inside equipment with power applied. Under certain conditions, dangerous potentials may exist when power has been turned off due to charges retained by capacitors. To avoid casualties, always remove power and discharge and ground a circuit before touching it.

### **Live Circuit Contact Procedures**

Never attempt to remove a person from a live circuit with your bare hands. To do so is to risk sure and sudden death. If a person is connected to a live circuit, the following steps should be taken:

- a. Call for help immediately

- b. De-energize the circuit, if possible.

- c. Use a wood or fiberglass hot stick to pull the person free of the circuit.

- d. Apply cardiopulmonary resuscitation (CPR) if the person has stopped breathing or is in cardiac arrest.

- e. Obtain immediate medical assistance.

### **Electrostatic Sensitive Devices**

Various circuit card assemblies and electronic components may be classified as Electrostatic Discharge (ESD) sensitive devices. Equipment manufacturers recommend handling all such components in accordance with the procedures described in Appendix A. FAILURE TO DO SO MAY VOID YOUR WARRANTY.

### Magnetic Media

Do not place or store magnetic media (tapes, discs, etc.) within ten feet of any magnetic field.

### **Related Technical Documentation**

| MANUAL NUMBER  | MANUAL TITLE                                      |  |

|----------------|---------------------------------------------------|--|

| 3A0-602204-363 | PMAC & PMAC2 Software Reference                   |  |

| 3A0-602598-363 | PMAC2-PC and PMAC2-Lite Hardware Reference Manual |  |

| 3A0-602415-363 | PMAC2-PC Ultralite Hardware Reference Manual      |  |

| 3A0-602413-363 | PMAC2-VME Hardware Reference Manual               |  |

| 3A0-602643-363 | PMAC2-VME Ultralite Hardware Reference Manual     |  |

### **Technical Support**

Delta Tau is happy to respond to any questions or concerns you have regarding PMAC. You can contact the Delta Tau Technical Support Staff by the following methods:

### By Telephone

For immediate service, you can contact the Delta Tau Technical Support Staff by telephone Monday through Friday. Our support line hours and telephone numbers are listed below.

### By FAX and E-Mail

You can FAX or E-Mail your request or problem to us overnight and we will deal with it the following business day. Our FAX numbers and E-Mail addresses are listed below. Please supply all pertinent equipment set-up information.

### **Bulletin Board Service (BBS)**

You can also leave messages on one of our Bulletin Board Services (BBSs). The BBSs are provided for our Customers, Distributors, Representatives, Integrators, et al. We invite you to use this service. You can download & upload files and read posted bulletins and Delta Tau newsletters. Messages may be left for anyone who is a member/user of the Bulletin Board System(s). All you need is a modem and Procomm-Plus or similar communications program. Many Download-Upload Protocols such as Z-Modem are supported.

### **World Headquarters**

Delta Tau Data Systems, Inc. 9036 Winnetka Avenue Northridge CA, 91324

### **Support Hot Line**

Monday through Friday 8:30am to 4:30pm PST Voice: (818) 998-2095 FAX: (818) 998-7807 BBS: (818) 407-4859

E-Mail: support@deltatau.com

### Eastern U.S. Office

Delta Tau Data Systems, Inc. 10754 Decoursey Pike Ryland Heights, KY 41015

#### **Support Hot Line**

Monday through Friday 8:30am to 4:30pm EST Voice: (606) 356-0600 FAX: (606) 356-9910 BBS: (606) 356-6662 E-Mail: support@deltatau.com

### **European Office**

Delta Tau Data Systems International Industrieweg 175, Suite 7 3044 AS Rotterdam, Netherlands

#### **Support Hot Line**

Monday through Friday 8:00am to 4:00pm GMT Voice: 31-10-462-7405

FAX: 31-10-245-0945

BBS: TBD

E-Mail: <u>bradped@xs4all.nl</u>

**BBS Settings:** Baud Rates: 1200 to 19.2 8 - data bits, 1 - stop bit, No Parity

# Basic Motor Setup on PMAC2

# **Controlling Motors**

PMAC2 has many modes for controlling motors. A major part of the initial setup of a PMAC2 is the hardware and software configuration to specify a specific mode of operation. The commonly used modes of operation are:

- ♦ Analog command of velocity-mode drives

- Analog command of torque-mode drives

- ♦ Analog command of sine-wave input drives

- ♦ Direct-PWM control of power-block drives

- Pulse-and-direction command of stepper or stepper-replacement servo drives

# **Hardware Setup**

The machine interface ports on the PMAC2 itself are not designed to be connected directly to drives, encoders, flags, etc. Almost always an interface board is required. Delta Tau provides a family of 2-axis interface boards (the ACC-8 family) that cover most common interfaces; large-volume users may want to design and build their own interface boards optimized for their own purposes. The interface boards currently available from Delta Tau are:

- <u>ACC-8E:</u> Dual analog output per axis for velocity, torque, or sinewave commands; encoder, hall, and optically isolated flag feedback; DIN-rail mountable

- ♦ <u>ACC-8F:</u> Direct PWM output; serial digital current feedback; encoder, hall, and optically isolated flag feedback; DIN-rail mountable

- ◆ <u>ACC-8FP:</u> Direct PWM output; serial digital current feedback; encoder, hall, and optically isolated flag feedback; panel-mountable

- <u>ACC-8K1:</u> Fanuc C/S-Series interface; direct PWM output, analog current feedback; encoder, hall, and optically isolated flag feedback; DIN-rail mountable

- <u>ACC-8K2:</u> Kollmorgen IPB interface; direct PWM output, analog current feedback; encoder, hall, and optically isolated flag feedback; DIN-rail mountable

- ♦ <u>ACC-8S:</u> Pulse-and-direction output; encoder feedback by option only; optically isolated flag feedback; DIN-rail mountable

There is a single flat-cable connection from the 100-pin JMACHn connector on the PMAC2 to the matching connector on the ACC-8 board. The details of the connection between the ACC-8 board and the drives, encoders, hall sensors (if any), and flags are covered in the appropriate ACC-8 manual and the *Hardware Setup* section for each mode description, below.

# **PMAC2** Parameter Setup

Several PMAC2 I-variables must be specified for proper operation of the card in the desired operating modes. This section simply lists the important variables; details of how to set them up are covered in the appropriate section of the User's Guide, and in the I-Variable Specification of the Software Reference.

### Parameters to Set Up Global Hardware Signals

I-variables in the range I900-I909 (I990-I999 for a PMAC2 Ultralite) control operation of PMAC2 global and multi-channel hardware operation. These variables form the control registers of the DSPGATE1 & 2 ASICs on the PMAC2.

I900 (I992 for an Ultralite) controls the maximum possible phase frequency (MaxPhase) for the card, and the PWM frequency for channels 1-4.

I901 (I997 for an Ultralite) controls the phase clock frequency for the card, the rate at which commutation and current-loop updates are done, by specifying the divide-down from MaxPhase.

I902 (I998 for an Ultralite) controls the servo clock frequency for the card, the rate at which command position interpolation and the position/velocity servo algorithms are executed.

I903 controls the hardware clock frequencies for channels 1-4; I907 controls the hardware clock frequencies for channels 5-8; I993 controls the hardware clock frequencies for supplementary channels 1\* and 2\* (the only channels on an Ultralite). These almost never need to be changed from the default.

I904 controls the PWM deadtime and PFM pulse width for channels 1-4; I908 does the same for channels 5-8; I994 does the same for supplementary channels 1\* and 2\* (the only channels on an Ultralite).

I905 controls the DAC strobe signal for channels 1-4; I909 does the same for channels 5-8.

Figure 2-1. PMAC2 Gate Array IC Clock Control

### Parameters to Set Up Per-Channel Hardware Signals

Each machine interface channel *n* on the PMAC2 has several setup I-variables to configure the outputs and the feedback for that channel. These variables form part of the control word for the channel in the DSPGATE1 ASIC.

The ten's digit of the I-variable specifies which channel is being controlled; for example I910 controls the encoder decode for Channel 1. The generic reference for the variable uses the letter n for the channel digit; I9n0 refers generally to the encoder decode variable for Channel n, where n = 1 to 8. Usually a given Channel n is used for the PMAC2 Motor x of the same number (i.e. n = x), but this does not have to be the case. (These variables are not active on Ultralite versions of PMAC2, because the Ultralite boards have a MACRO ring interface instead of the local machine interface channels.)

The most important of these variables are I9n0 and I9n6. I9n0 specifies the encoder decode for channel n, quadrature or pulse-and-direction, including the direction sense. I9n6 specifies which output signal modes are used for Channel n: DAC for analog control, PWM (pulse width modulation) for direct power-block control, and/or PFM (pulse frequency modulation) for stepper motor control. Refer to the instructions for setup of the specific mode you are using, below, or the I-variable specification in the Software Reference for details.

Figure 2-2. PMAC2 Gate Array IC Output Channel

Figure 2-3. PMAC2 Gate Array IC Encoder/Flag Channel

Figure 2-4. PMAC2 Gate Array IC Input Channel

### **Parameters to Set Up Motor Operation**

Each Motor x has setup I-variables to permit specific software configuration of that motor's control algorithms. The hundred's digit of the I-variable specifies which motor is being configured; for example I100 activates or de-activates Motor 1. The generic reference for the variable uses the letter x for the motor digit; Ix00 refers generally to the activation variable for Motor x, where x = 1 to 8.

Most of the software configuration of a motor involves setting proper values for these variables, as explained in the following sections. This section has a quick survey of the key variables, and the variables that are common to all modes.

### **Activating the Motor**

The Ix00 motor activation parameter must be set to 1 for any motor that is to be used on PMAC2. It should be set to 0 for any motor that is not used, so PMAC2 will not waste computation time on that motor.

### **Does PMAC Commutate the Motor?**

The Ix01 commutation enable parameter must be set to 1 if PMAC2 is performing the commutation and/or digital current loop for the motor. It must be set to 0 for any motor if PMAC2 is performing neither the commutation nor digital current loop for the motor.

### **Command Output Address**

Ix02 specifies the address(es) of the register(s) to which PMAC2 writes the command output(s) for the motor. The default values of Ix02 contain the address of the A command register in DSPGATE1. For the machine interface channel n, where n = x; these values are suitable for analog output modes with and without commutation, and for direct PWM control.

Figure 2-5. DSP Gate Command Output Registers

### **Position-Loop Feedback Address**

Ix03 specifies the address of the register PMAC2 reads for the position-loop feedback for the motor. This is almost always the address of a processed feedback data register in the encoder conversion table. With the default conversion table, the default values of Ix03 specify the processed data for Encoder n, where n = x; these values are suitable for most applications, regardless of the command output mode. Refer to the User's Guide section on the encoder conversion table for more information.

### **Velocity-Loop Feedback Address**

Ix04 specifies the address of the register PMAC2 reads for the velocity-loop feedback for the motor. It works just like Ix03, and contains the same address as Ix03 unless dual feedback is used for the motor.

### Flag Address

Ix25 specifies the address of the register PMAC2 uses for its flag information. The flags used are HOMEn, PLIMn, MLIMn, USERn, FAULTn, AENAn, CHCn, CHTn, CHUn, CHVn, and CHWn. The default values of Ix25 specify the flag register for machine interface channel n, where n = x.

### **Power-Up Mode**

Ix80 specifies whether PMAC will try to control the motor immediately on power-up/reset, performing a phasing search if necessary; or whether it will put the motor in a killed state on power-up/reset and await a command to enable the motor.

### **Commutation Parameters**

If Ix01 is set to 1, variables Ix70 to Ix84 for the motor must be set properly to perform the commutation and/or current loop closure in the PMAC2. The settings of these variables are explained in one of the following sections: *Setting Up PMAC2 for Direct PWM Control*, or *Setting Up PMAC2 for Sine-Wave Output Control*.

# Setting Up PMAC2 for Direct PWM Control

### Introduction

The instructions given in this section are for the first-time setup with an otherwise unknown interface. For a given interface to the drive, motor and feedback device, many parts of the setup will simply be taken from a list, and will not have to be tested, or tested as thorougly as described in this chapter. A list of configuration-specific settings should come with the manual for each particular interface or drive. Subsequent versions of the same setup should be even easier.

One of PMAC2's important new features is the ability to close motor current loops digitally. That is, the current control loop is closed by using digital computation operating on numerical values in registers rather than by using analog processing operating on voltage levels with op-amps. The digital techniques bring many advantages:

- ♦ There is no need for pot tweaking or personality modules

- ♦ There is no drift over temperature or time

- Computer analysis and autotuning are possible

- Gain values are easily stored for backup and copying onto other systems

- ♦ Adaptive techniques are possible.

When performing digital current loop closure on the PMAC2, several hardware and software features must be set up properly to utilize the digital current loop and direct PWM outputs correctly. The following section details how to perform this setup manually. Delta Tau has new expert system PC software running under Microsoft Windows to walk you through this setup step-by-step, vastly simplifying the process.

# **Direct PWM Control Of Amplifiers**

This section explains how to set up PMAC2 for direct PWM control of amplifiers. In this mode, PMAC2 performs all of the control tasks for the motor, including commutation and digital current loop closure. The amplifier performs only the power conversion task. In this mode, PMAC2 outputs PWM voltage commands for each phase of the motor. If you are not using PMAC2 to perform this task for any of your motors, you may skip this section. Simply make sure that Ix82 is set to 0 for all of your activated motors, so PMAC2 will not try to close the current loop for them.

# **Digital Current Loop Principle of Operation**

Traditionally, motor phase current loops have been closed in analog fashion, with op-amp circuits creating phase voltage commands from the difference between commanded and actual phase current signal levels. These analog phase voltage commands are converted to PWM format through analog comparison to a saw tooth waveform.

PMAC2 permits digital closure of the motor current loops, mathematically creating phase voltage commands from numerical registers representing commanded and actual current values. These numerical phase voltage commands are converted to PWM format through digital comparison to an up/down counter that creates a digital saw tooth waveform. The analog current measurements must be converted to digital form with ADCs before the loop can be closed.

### **Frames of Reference**

A very important advantage of the digital current loop is its ability to close the current loops in the field frame. To understand this advantage, some basic theoretical background is required.

In a motor, there are three frames of reference that are important. The first is the stator frame, which is fixed on the non-moving part of the motor, called the stator. In a brushless motor, the motor armature windings are on the stator, so they are fixed in the stator frame.

The second frame is the rotor frame, which is referenced to the mechanics of the moving part of the motor, called the rotor. This frame, of course, rotates with respect to the stator. For linear brushless motors, this is actually a translation, but because it is cyclic, we can easily think of it as a rotation.

The third frame is the field frame, which is referenced to the magnetic field orientation of the rotor. In a synchronous motor such as a permanent-magnet brushless motor, the field is fixed on the rotor, so the field frame is the same as the rotor frame. In an asynchronous motor such as an induction motor, the field slips with respect to the rotor, so the field frame and rotor frame are separate.

### **Working in the Field Frame**

The physics of motor operation are best understood in the field frame. A current vector in the stator that is perpendicular to the rotor field (that is, current in the stator that produces a magnetic field perpendicular to the rotor magnetic field) produces torque. This component of the stator current is known as quadrature current. The output of the position/velocity loop servo algorithm is the magnitude of the commanded quadrature current. For diagnostic purposes on PMAC2, the O command can be used to set a fixed quadrature current command.

A current vector in the stator that is parallel to the rotor field induces current in the rotor that changes the magnetic field strength of the rotor (when the stator and rotor field are rotating relative to each other). This component of the stator current is known as direct current. For an induction motor, this is required to create a rotor magnetic field. For a permanent-magnet brushless motor, the rotor magnets always produce a field, so direct current is not required, although it can

be used to modify the magnetic field strength. On PMAC2, parameter Ix77 for motor x determines the magnitude of the direct current.

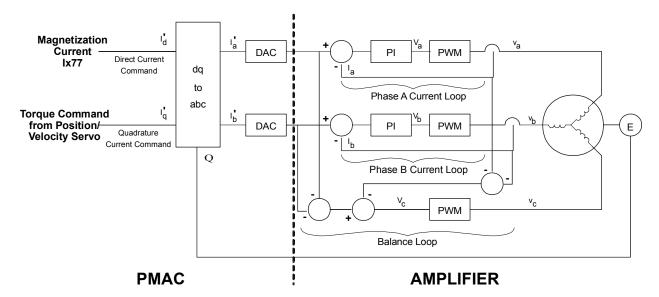

### **Analog Loops in the Stator Frame**

In an amplifier with an analog current loop, the closure of the loops on the stator windings must be closed in the stator frame. The current measurements are in the stator frame and analog circuitry has no practical way to transform these. In such a system, the current commands must be transformed from the field frame in which they are calculated to the stator frame, and converted to voltage levels representing the individual stator phase current commands. These are compared to other voltage levels representing the actual stator phase current measurements.

As the motor is rotating, and/or the field is slipping, these current values, command and actual, are AC quantities. Overall loop gain and system performance, are reduced at high frequencies (high speeds). The back EMF phase voltage, which acts as a disturbance to the current loop, is also an AC quantity. The current loop integral gain or lag filter, which is supposed to overcome disturbances, falls well behind at high frequencies.

Figure 3-1. PMAC/PMAC2 Commutation with Analog Current Loop

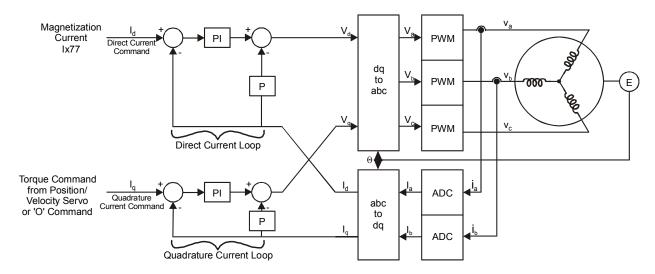

### **Digital Loops in the Field Frame**

In an system with a digital current loop, it is possible to close the current loops in the field frame (not all such systems do, however). Instead of transforming the current commands from field frame to stator frame before closing the loop, the actual current measurements are transformed from stator frame to field frame. In the field frame, a direct-current loop is closed, and a quadrature current loop is closed. This produces a direct-voltage command, and a quadrature-voltage command; these are transformed back into the stator frame to become phase-voltage commands, which are implemented as PWM values.

The direct and quadrature current values are DC quantities, even as the motor is rotating and the field is slipping. Therefore, the high-frequency limitations of

the servo loop are irrelevant. This provides significantly improved high-speed performance from identical motors and power electronics.

Figure 3-2. PMAC2 Commutation with Digital Current Loop

PMAC2 has a PI (proportional-integral) digital current loop. There is only one set of gains, which serves for both the direct current loop and the quadrature current loop. Tuning is best done on the direct current loop, because this will generate no torque, and therefore no movement. The current-loop autotuner in the PMAC Executive program uses the direct current loop to tune. This is valid even for permanent-magnet brushless motors where no direct current will be used in the actual application. It is important to remember that current loop performance is not load-dependent, so the motor does not need to be attached to the load during the tuning process (for position/velocity loop tuning, the load does need to be attached).

### Hardware Setup

Usually the hardware connection between PMAC2 and the digital amplifier is made with integrated cables, either directly to the amplifier, or to an interface board. The following section details the individual signal line connections for those users who do not have an integrated connection solution. If you have a pre-designed connection system, refer to the appropriate manual for connection information.

The connection between PMAC2 and the direct PWM digital amplifier is almost always made through an interface board. Typically this interface board works for 2 axes, connecting with a short 100-strand flat cable to one of PMAC2's machine connectors. The interface board has connectors to the amplifiers, to the position feedback sensors, and to any flags used (overtravel limits, home, etc.).

Existing Delta Tau boards for this style of connection at the time of this writing are:

♦ ACC-8F PWM Interface (requires A/D converters in the amplifier)

♦ ACC-8K1 Fanuc C- & S-Series Drive Interface

♦ ACC-8K2 Kollmorgen IPB

Drive Interface

All of the digital amplifier interface lines on PMAC2 itself are digital

5V signals. There is no optical isolation on PMAC2; any optical isolation must be provided on an interface board or in the amplifier.

### **PWM Signal Outputs**

When PMAC2's digital current loop is used, the format of the output commands is virtually always digital pulse-width-modulated (PWM) signals. For each machine interface channel, PMAC2 has 3 pairs of top and bottom PWM signals, which can be used for the half-bridges of a 3-phase motor. Each of these 6 output signals is a differential line-driver pair, for a total of 12 PWM pins. These pins are named:

- ◆ PWMATOPn+PWMATOPn-(Phase A top transistor command)

- PWMABOTn+PWMABOTn-(Phase A bottom transistor command)

- PWMBTOPn+PWMBTOPn-(Phase B top transistor command)

- ♦ PWMBBOTn+PWMBBOTn-(Phase B bottom transistor command)

- PWMCTOPn+PWMCTOPn-(Phase C top transistor command)PWMCBOTn+PWMCBOTn-(Phase C bottom transistor command)

where n is the PMAC2 channel number. These pins have alternate uses as DAC signals and pulse-and-direction outputs; PMAC2 parameters are used to configure them as PWM outputs (see below).

### **ADC Interface Signals**

The on-board multiplexed Option 12 ADCs are not suitable for current-loop feedback.

The actual phase current information is almost always brought in from serial analog-to-digital converters (ADCs). For a multi-phase motor, this information is brought back for two of the phases, what PMAC calls the A and B phase. These ADCs are not on the PMAC2; they are either in the amplifier, or on the interface board. Four digital interface signals are required for each pair of ADCs; the two serial inputs, an output clock, and an output strobe. Each of these signals is differential, for a total of 8 pins. These pins are named:

- ◆ ADC\_DAAn+ADC\_DAAn-(Phase A ADC serial input data)

- ADC DABn+ADC DABn-(Phase B ADC serial input data)

- ADC CLKn+ADC CLKn-(ADC clock output)

- ♦ ADC\_STBn+ADC\_STBn-(ADC strobe output)

where n is the PMAC2 channel number. While each channel has its own pins for the clock and strobe outputs, the signals are actually common for 4 channels (1-4 and 5-8).

### **PWM/ADC Phase Matching**

The current data brought back into PMAC2's Phase A input must be for the motor phase commanded by PMAC2's Phase A PWM output, whatever this phase is called on the motor and drive. The current data brought back into PMAC2's Phase B input must be for the motor phase commanded by PMAC2's Phase B PWM output, whatever this phase is called on the motor and drive.

This may mean that PMAC2's name for the phase may not match the motor's and drive's name for the phase. For example, for a motor/drive system that proivides current feedback on Phases A and C, PMAC2's PWM Phase B outputs would be connected to the drive's Phase C PWM inputs, the drive's Phase C current feedback would be connected to PMAC2's Phase B ADC inputs, and PMAC2's Phase C outputs would be connected to the drive's Phase B PWM inputs.

#### **Amplifier Enable and Fault Interface**

There is an amplifier enable/disable output and an amplifier fault input for each motor. Both signals are differential, for a total of 4 lines: AENAn+, AENAn-, FAULTn+, and FAULTn-. These signals are almost always part of the amplifier cable and connector.

#### **Supplemental Flags**

There are five supplemental flag inputs to PMAC2 for each motor that can be used for several purposes: T, U, V, W, and USER. The actual signal names are CHTn, CHUn CHVn, CHWn, and USERn. These are single-ended inputs, pulled up to +5V in the PMAC2.

These flag inputs can be used for low-resolution absolute motor position to prevent the need for a power-on phasing search on a synchronous motor. The U, V, and W inputs are commonly used for the hall-effect commutation inputs of a brushless motor. Some motors such as Fanuc have low-resolution binary absolute tracks on their encoders that can be brought in on T, U, V, and W.

Another use for these flags is as a fault code. T, U, V, and W can serve as a 4-bit fault code to tell PMAC why the drive faulted.

A third use for these flags is sub-count position information when interpolating from an analog encoder. PMAC2 can accept up to 5 bits of fractional information on T, U, V, W, and USER, with T as the most significant bit, and USER as the least significant bit.

With external multiplexing, it is possible to use these flags for more than one purpose. For example, they could be used to read hall-effect sensors on power-up, sub-count information in normal operation, and fault codes when the amplifier has faulted.

#### **Other Signals**

If the JMACH connector on PMAC2 connects directly to the amplifier without any interface board, non-amplifier signals for that motor must be passed through the amplifier, even if they are not used by the amplifier. This includes , such as encoder, home and limit flags, and hall-effect inputs.

# **PMAC2** Parameter Setup

Much of the PMAC2 interface hardware is software-configurable through I-variables. This section provides basic information on each of the I-variables that is important in this type of application. There is a detailed description of each I-variable in the Software Reference.

#### Parameters to Set up Global Hardware Signals

#### PWM Frequency Control: 1900, 1906

Set PMAC2 I-variable I900 to define the PWM frequency you want on machine interface channels 1-4 (typically motors 1-4) according to the equation:

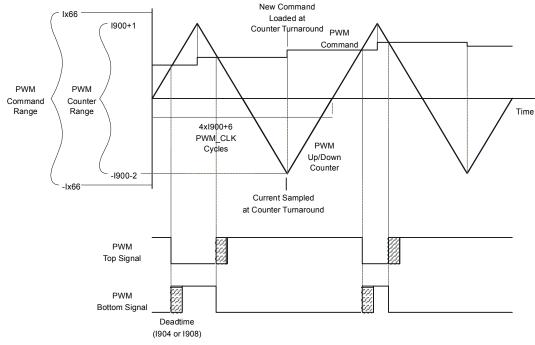

$$I900 = \inf \left( \frac{117,964.8kHz}{4*PWMFreq(kHz)} - 1 \right)$$

The frequency should be set within the specified range for the drives controlled by PMAC2. Too high a frequency can lead to excessive drive heating due to switching losses; too low a frequency can lead to lack of responsiveness, excess acoustic noise, possible physical vibration, and excessive motor heating due to high current ripple.

I906 controls the PWM frequency of machine interface channels 5-8 by the same equation. This frequency does not have to be the same as the frequency for channels 1-4, but it does have to have a synchronous relationship with the phase clock derived from the PWM 1-4 frequency with I901. The following relationship must hold for proper operation of channels 5-8:

$$2*\frac{PWM[5-8]Freq}{PhaseFreq} = \{Integer\}$$

I900 also sets the frequency of the MaxPhase clock to twice the PWM frequency. The MaxPhase clock is the highest frequency at which PMAC2's phase update tasks, which include phase commutation and digital current loop closure, can operate. Note that any change to I900 automatically changes the phase and servo clock frequencies.

#### Phase Clock Frequency Control: I901

I901 determines how the actual PHASE clock is generated from the MaxPhase clock, using the equation

$$PhaseFreq(kHz) = \frac{MaxPhaseFreq(kHz)}{I901 + 1}$$

Any change to the value of 1901 also automatically changes the servo clock frequency.

Every phase clock cycle, PMAC closes the digital current loop and performs the commutation for motors that have been configured for these algorithms.

I901 is an integer value with a range of 0 to 15, permitting a division range of 1 to 16. Typically, the PHASE clock frequency is in the range of 8 kHz to 12 kHz.. The 60 MHz PMAC2 is capable of performing commutation and digital current loop for 8 axes at up to 12 kHz; the 40 MHz is capable of doing this for 8 axes at up to 9 kHz, or for 6 axes at up to 12 kHz.

Generally the phase clock frequency that fits within the 8 to 12 kHz range within PMAC2's computation capabilities is chosen. Sometimes the actual PWM frequency is adjusted slightly to provide a suitable phase clock frequency.

For example, on large drives set up for 5 kHz PWM, the MaxPhase frequency is 10 kHz, so an I901 value of 0 sets the phase clock frequency to 10 kHz. On smaller drives set up for 18 kHz PWM, the MaxPhase frequency is 36 kHz, so an I901 value of 2 sets the phase clock frequency to 12 kHz, or a value of 3 sets 9 kHz.

#### Servo Clock Frequency Control: 1902

I902 determines how the SERVO clock is generated from the PHASE clock, using the equation

$$ServoFreq(kHz) = \frac{PhaseFreq(kHz)}{I902 + 1}$$

I902 is an integer value with a range of 0 to 15, permitting a division range of 1 to 16. On the servo update, which occurs once per SERVO clock cycle, PMAC2 updates commanded position (interpolates) and closes the position/velocity servo loop for all active motors, whether or not commutation and/or a digital current loop is closed by PMAC2. Typical servo clock frequencies are 1 to 4 kHz.

I10 tells the PMAC2 interpolation routines how much time there is between servo clock cycles. It must be changed any time I900, I901, or I902 is changed. I10 can be set according to the formula:

$$I10 = \frac{640}{9} (2 * I900 + 3)(I901 + 1)(I902 + 1)$$

#### Hardware Clock Frequency Control: 1903, 1908

I903 determines the frequency of four hardware clock signals use for machine interface channels 1-4; I907 does the same for machine interface channels 5-8. These can probably be left at the default values. The four hardware clock signals are SCLK (encoder sample clock), PFM\_CLK (pulse frequency modulator clock, DAC\_CLK (digital-to-analog converter clock), and ADC\_CLK (analog-to-digital converter clock).

Only the ADC\_CLK signal is directly used with the digital current loop, to control the frequency of the serial data stream from the current-loop ADCs. The ADC clock frequency must be at least 96 times higher than the PWM frequency, but it must be within the capability of the serial ADCs Refer to the I903 and I908 descriptions for detailed information on setting these variables.

The encoder SCLK frequency should be at least 20% greater than the maximum count (edge) rate that is possible for the encoder on any axis. Higher SCLK frequencies than this minimum may be used, but these make the digital delay anti-noise filter less effective.

#### **PWM Deadtime Control: 1904, 1908**

I904 determines the PWM deadtime between top and bottom signals on for machine interface channels 1-4; I908 does the same for machine interface channels 5-8. I904 and I908 have a range of 0 to 255, and the deadtime is 0.135 usec time the I-variable value. The deadtime should not be set smaller than the recommended minimum for the drive, or excessive drive heating could occur. Too large a deadtime value can cause unresponsive performance. The default value of 15, which produces a deadtime of 2.0 usec, is large enough to protect almost all drives, and small enough not to create unresponsive performance unless PWM frequencies are extremely high.

#### Parameters to Set Up Per-Channel Hardware Signals

For each machine interface channel n (n = 1 to 8) used for PWM outputs, a few I-variables must be set up properly.

I9n0 must be set up to decode the commutation encoder properly. Almost always a value of 3 or 7 is used to provide times-4 decode of a quadrature encoder. The difference between 3 and 7 is the direction sense of the encoder; a test described below allows you to evaluate the direction you want.

In 19n6 must be set to 0 to specify all 3 outputs A, B, and C are in PWM format for a 3-phase motor. If only 2 PWM output pairs are used (for a 1, 2, or 4-phase motor), In 6 could also be set to 2, permitting the C-outputs to be PFM format for other uses.

I9n7 controls whether the PWM output signals are inverted or not. At the default value of 0 (non-inverted) the transistor-on signals are high (+5V) on the PWM+ lines, and low on the PWM- lines. This setting will be used for almost all PWM drives.

#### **Parameters to Set Up Motor Operation**

Direct PWM control of brush motors with digital current loop utilizes PMAC2's commutation algorithms even though the motor does not require electronic commutation; Ix01 must be set to 1 for this case.

Several I-variables must be set up for each Motor x to enable and configure the digital current loop for that motor. Of course, Ix00 must be set to 1 for any active motor, regardless of whether digital current loop is used for that motor or not

#### **Commutation Enable: Ix01**

Ix01 is set to 1 to instruct PMAC2 to perform the phase commutation for this motor. If PMAC2 is performing the digital current loop closure, it must also perform the phase commutation for the motor.

#### **Command Output Address: Ix02**

Ix02 instructs PMAC2 where to place its output commands for Motor x by specifying the address. The default values of Ix02 use the PWM registers A, B, and potentially C for Machine Interface Channel n, where n=x. Ix02 seldom needs to be changed from the default value for PWM applications. The actual address specified is that of the PWM A register; PMAC2 then automatically writes to the B and C registers as well. The values typically used are:

Table 3-1. PWM Command Output Addresses (Y-registers)

| CHAN# | 1      | 2      | 3      | 4      | 5      | 6      | 7      | 8      |